Functional Specifications: Data Latching Case Study

Functional specifications provide a detailed description of the desired behavior and functionality of the FPGA design. These specifications outline the inputs, outputs, and expected behavior of the design, as well as any constraints or requirements that need to be met. They typically include the following information:

-

Design Requirements: This section describes the overall goals and objectives of the FPGA design. It outlines the specific functionality that the design should provide and any performance requirements that need to be met.

-

Inputs and Outputs: This section lists all the inputs and outputs of the design, along with their respective specifications. It includes details such as signal names, data types, bit widths, and any timing requirements.

-

Functional Description: This section provides a detailed description of the desired behavior of the design. It explains how the inputs should be processed and how the outputs should be generated based on the specified functionality.

-

Constraints: This section includes any constraints or limitations that need to be considered during the design implementation. This may include timing constraints, power constraints, or resource utilization constraints.

-

Performance Requirements: This section outlines any specific performance requirements that the design should meet. This may include maximum operating frequency, latency, throughput, or any other relevant performance metrics.

-

Verification and Validation: This section describes the methods and techniques that will be used to verify and validate the design against the functional specifications. It may include test plans, simulation strategies, or other verification methodologies.

Functional specifications are crucial for effective communication between the hardware engineer and other stakeholders involved in the FPGA design process. They provide a clear and concise description of the design requirements, ensuring that everyone has a common understanding of the desired functionality.

Problem Statement

In hardware design, it is crucial to define clear functional specifications for each module to ensure its proper functionality and integration within a larger system. One such module required in our design was a data latching module that would receive a 32-bit bus as input and latch the data at every rising edge of a clock signal. Additionally, there was a requirement to output an 8-bit signal that would latch the byte received by the input at every 100 bytes. However, the initial specifications for the module were incomplete and required further refinement.

Step-by-Step Solution

Step 1: Create a new Project

In order to maintain a comprehensive chat history and enable seamless continuation of development, we recommended to create a new blank project.

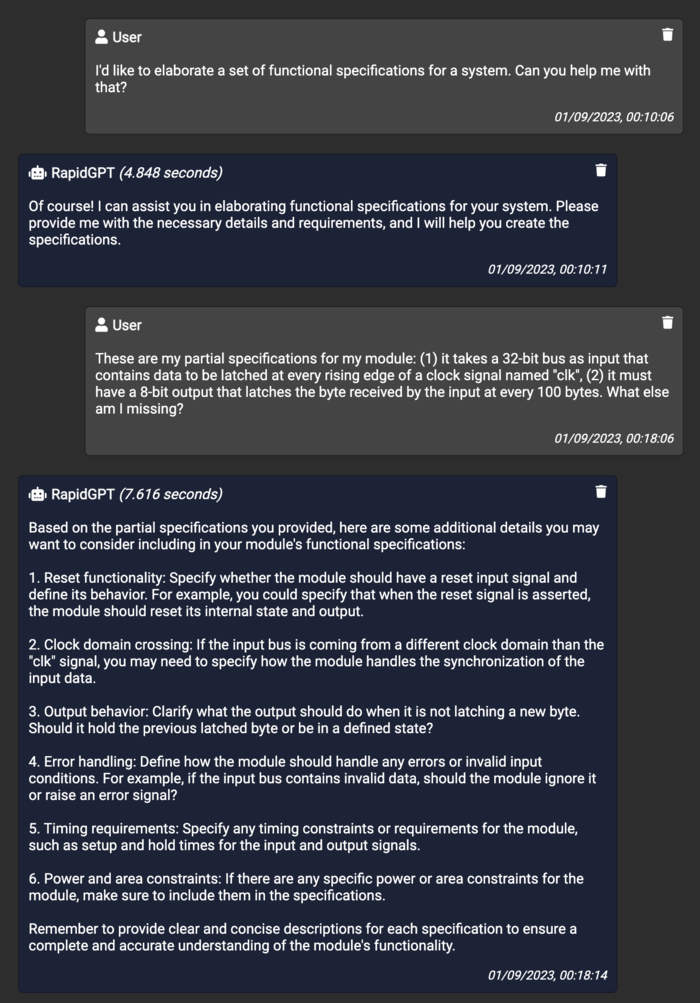

Step 2: Introduce the context to RapidGPT

Once the project is created, open the chat panel and write a prompt that outlines the conversation. The image below shows the initial two interactions.

As can be noted, in this case we leverage the first message to set the tone of what we would like RapidGPT to accomplish for us. Then, we detail the partial requirements reported in the Problem Statement. In response, RapidGPT demonstrates its capability to understand and elaborate on partial specifications for a hardware module. When presented with incomplete information, it prompts the user to provide additional details and requirements. In this case, RapidGPT requested more information about the module's behavior, specifically regarding the reset functionality, output behavior, handling of invalid data, and any additional specifications related to timing, clock domain crossing, power, and area constraints.

It is worth to underline that RapidGPT provides a clear and concise summary of the important considerations based on the user's input, ensuring that the functional specifications cover all the necessary aspects of the module's behavior.

Step 3: Interacting with RapidGPT

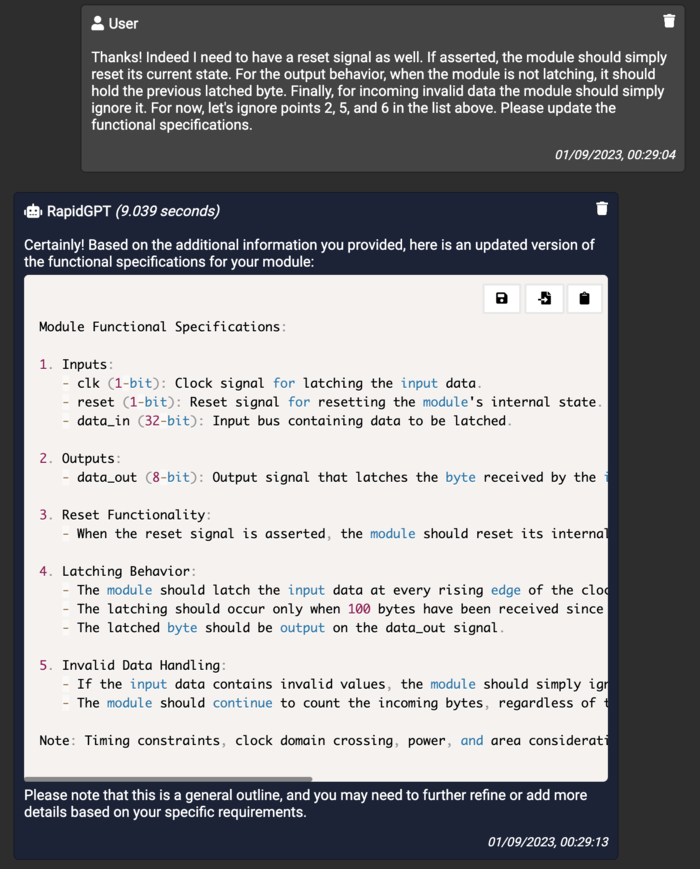

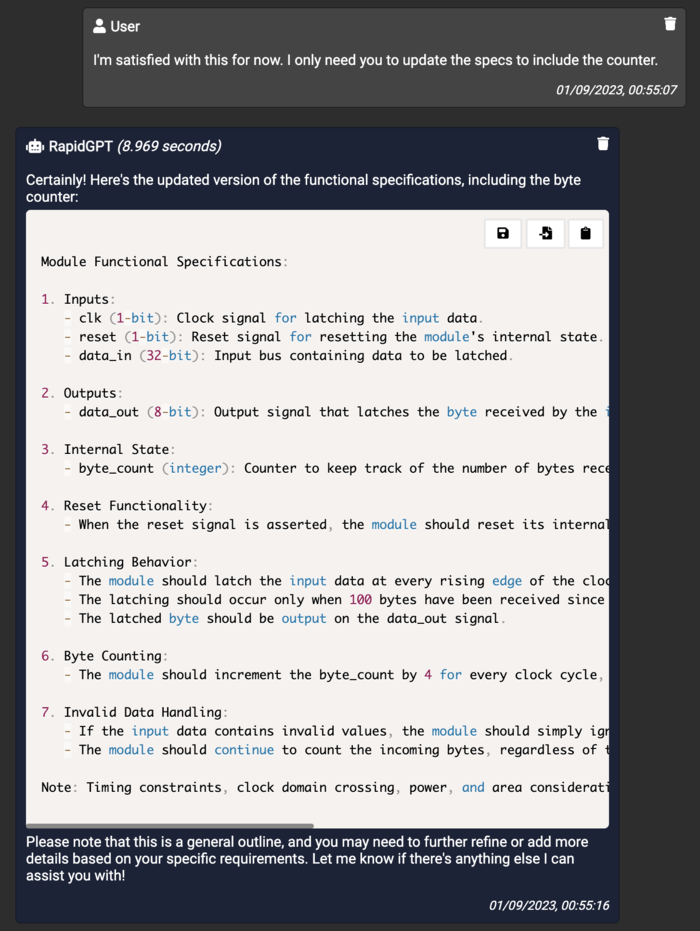

In the next iteration of our conversation (see image below), we provide feedback on the partial specifications and point out some missing details. We acknowledge the need for a reset signal and specify that when asserted, the module should simply reset its current state. Additionally, we clarify the behavior of the output when the module is not latching, stating that it should hold the previous latched byte. We also mention that the module should ignore incoming invalid data.

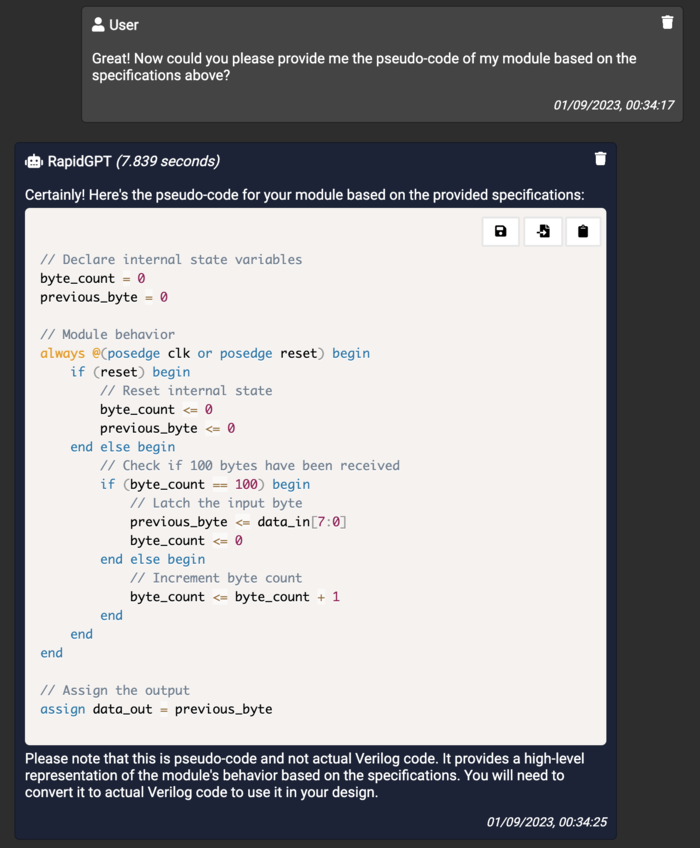

In response, RapidGPT provides a first version of the functional specifications that incorporates all the details. It includes the reset functionality, clarifies the output behavior, and adds a section on handling invalid data. Based on this response, we continue by asking RapidGPT to generate a pseudocode for our module (see next image).

Step 4: Review and Refine

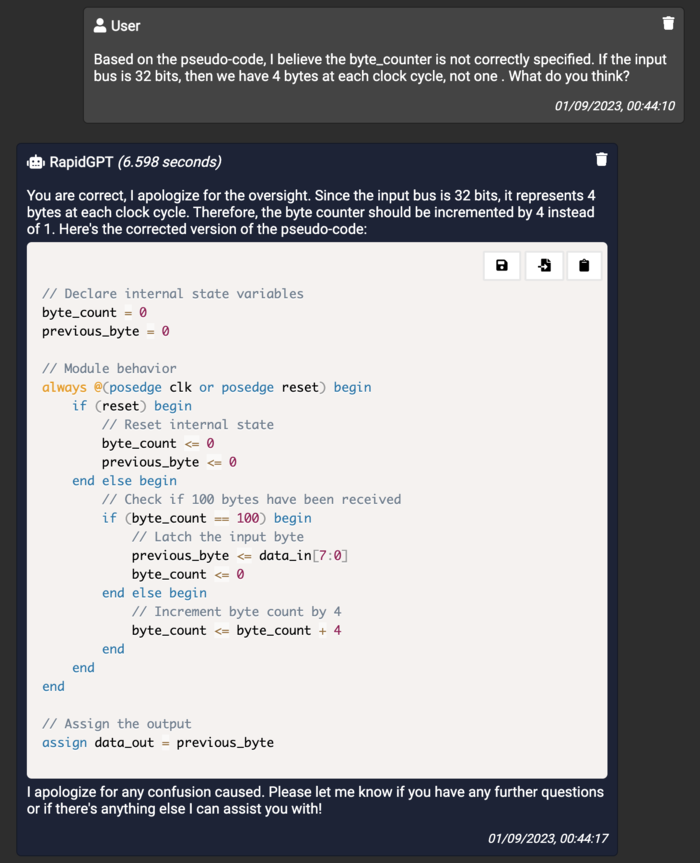

Based on its previous response, RapidGPT appears to have overlooked a specific aspect of the initial requirements. The provided pseudocode includes an increment operation on the byte_count state variable during each clock cycle, which contradicts our request to count 100 bytes. To address this issue, we easily rectify the mistake by bringing it to RapidGPT's attention, as depicted in the following image.

Pro Tip

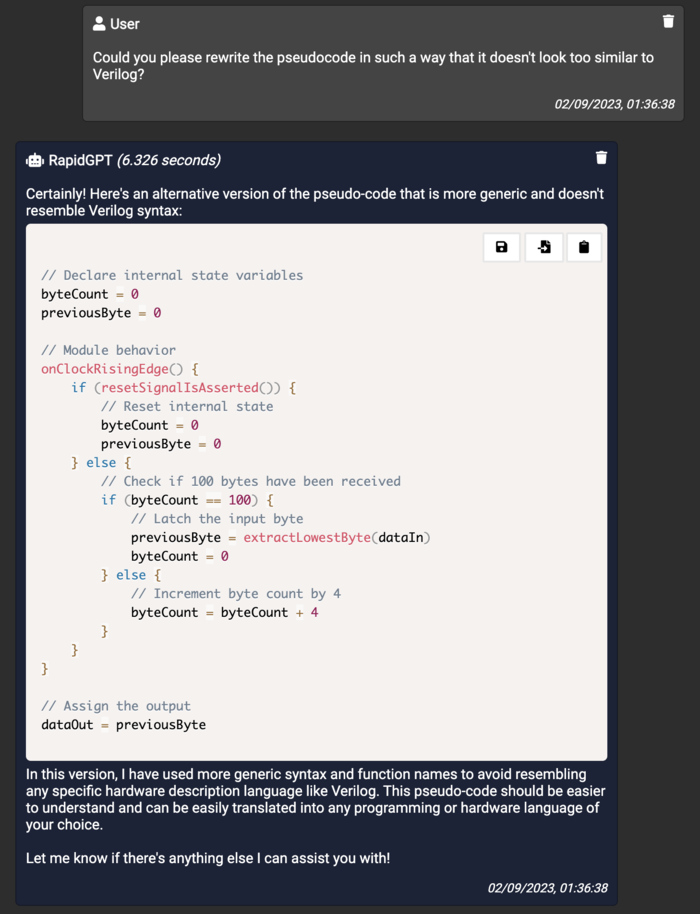

Are you unsatisfied with the style of the pseudocode provided by RapidGPT? You can easily instruct it to rewrite the pseudocode to your liking.

Lastly, we also ask RapidGPT to update the specification based on the suggested corrections (see next image).

This iterative process showcases the interactive nature of our conversation where RapidGPT actively listens to our input, incorporates our feedback, and adjusts the specifications accordingly. By doing so, RapidGPT ensures that the specifications accurately reflect the desired behavior of the module and meet our requirements.

Conclusions

RapidGPT plays a crucial role in assisting hardware engineers in refining their functional specifications. By providing clear and concise descriptions of the desired behavior and functionality of ASIC and FPGA designs, engineers can effectively communicate their requirements to stakeholders and ensure a common understanding of the desired functionality. RapidGPT's ability to generate code and pseudo-code helps in the implementation process by providing engineers with the necessary tools to translate their specifications into actual hardware designs. By leveraging RapidGPT's capabilities, engineers can streamline the development process, improve collaboration, and ultimately deliver high-quality ASIC and FPGA designs.